|

| www..hardware-system.com |

One can visualize a port as consisting of two units; internal to the module and external to the module. The internal and external units are connected as shown in the figure beside.

There are rules governing port connections when modules are instantiated within other modules. The Verilog simulator complains if any port connection rules are violated.

Inputs

Internally, input ports must always be of the type net. Externally, the input can be connected to a variable which is a reg or a net.

Outputs

Internally, outputs ports can be of the type reg or net. Externally, the outputs must always be connected to a net. They cannot be connected to a reg.

Inouts

Internally, inout ports must always be of the type net. Externally, inout ports must always be connected to a net.

It is legal to connect internal and external items of different sizes when making inter-module port connections. However, a warning is typically issued that the widths do not match.

Unconnected Ports

Verilog allows ports to remain unconnected. For example, certain output ports might be simply for debugging, and we might not be interested in connecting them to the external signals. We can let the port remain unconnected by instantiating a module as shown below.

-------------------------------------------------------------------------------------------------------

full_add4 fa0 (SUM, , A, B, C_IN); // Output port c_out is unconnected

--------------------------------------------------------------------------------------------------------

Example of illegal port connection

To illustrate port connection rules, assume that the module full_add4 is instantiated in the stimulus block Top. The following code is an example of illegal port connection in Verilog coding.

-----------------------------------------------------

module Top;

//Declare connection variables

reg [3:0] A, B;

reg C_IN;

reg [3:0] SUM;

wire C_OUT;

full_add4 fa0 (SUM, C_OUT, A, B, C_IN); // instantiate full_add4, call fa0

-

-

<stimulus>

-

-

endmodule

-------------------------------------------------------

Illegal connection because output port

SUM in the module

full_add4 is connected to a register variable

SUM in module

Top. This problem is rectified if the variable

SUM is declared as a

net (

wire). Read related topic on

port connections more detail at

Port Declaration in Verilog HDL.

Reference:

- Verilog HDL, A guide to Digital Design and Synthesis, 2nd edtion, Samir Palnitkar, SunSoft Press - A Prentice Hall Title.

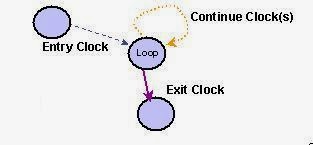

In this session, we will design and discuss a traffic light controller using Verilog and finite state machine approach. Consider a controller for traffic at the intersection of a main street and a side street as shown in the figure beside.

In this session, we will design and discuss a traffic light controller using Verilog and finite state machine approach. Consider a controller for traffic at the intersection of a main street and a side street as shown in the figure beside.