There are four types of looping statements in Verilog: while, for, repeat, and forever. The syntax of these loops is very similar to the syntax of loops in the C programming language. All looping statements can appear only inside an initial or always block. Loops may contain delay expressions.

While Loop

The keyword while is used to specify this loop. The while loop executes until the while-expression is not true. If the loop is entered when the while-expression is not true, the loop is not executed at all. Each expression can contain any operators.

Any logical expression can be specified with any operators. If multiple statements are to be executed in the loop, they must be grouped typically using keywords begin and end. Example below illustrates the use of the while loop.

// Illustration 1: Increment count from 0 to 127. Exit at count 128.

// Display the count variable.

----------------------------------------------------------------------------

integer count;

initial

begin

count = 0;

while (count < 128) // Execute loop till count 127, exit at count 128initial

begin

count = 0;

begin

$display("Count = %d", count);

count = count + 1;

$display("Count = %d", count);

count = count + 1;

end

end

// Illustration 2: Find the first bit with a value 1 in flag (vector variable)

----------------------------------------------------------------------------

`define TRUE 1'b1';

`define FALSE 1'b0';

reg [15:0] flag;

integer i; // integer to keep count

reg continue;

initial`define FALSE 1'b0';

reg [15:0] flag;

integer i; // integer to keep count

reg continue;

begin

flag = 16'b 0010_0000_0000_0000;

i = 0;

continue = 'TRUE;

flag = 16'b 0010_0000_0000_0000;

i = 0;

continue = 'TRUE;

while((i<16) && continue) // Multiple conditions using operators

end

end

begin

if (flag[i])

begin

$display("TRUE bit at element number %d", i);

continue = 'FALSE;

if (flag[i])

begin

$display("TRUE bit at element number %d", i);

continue = 'FALSE;

end

i = i + 1;end

For Loop

The keyword for is used to specify this loop. The for loop contains three parts:- An initial condition

- A check to see if the terminating condition is true

- A procedural assignment to change value of the control variable

// For Loop

----------------------------------------------------------------------------

integer count;

initial

for (count=0; count < 128; count = count + 1) initial

$display("Count = %d",count);

Note, however, that the while loop is more general-purpose than the for loop. The for loop cannot be used in place of the while loop in all situations.

for loops can also be used to initialize an array or memory, as shown below.

// Initialize array elements

----------------------------------------------------------------------------

`define MAX_STATES 32

integer state [0:'MAX_STATES-1];

integer i;

initialinteger state [0:'MAX_STATES-1];

integer i;

begin

for(i=0; i<32; i =i+2) // initialize all even locations with 0

state[i] = 0;

for(i=1; i<32; i =i+2) // initialize all odd locations with 1

end for(i=1; i<32; i =i+2) // initialize all odd locations with 1

state[i] = 1;

for loops are generally used when there is a fixed beginning and end to the loop. If the loop is simply looping on a certain condition, it is better to use the while loop.

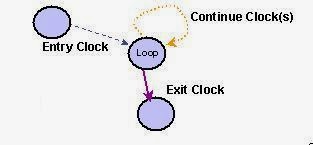

repeat loop and forever loop will be discussed in the next discussion.

Reference:

- Verilog HDL, A guide to Digital Design and Synthesis, 2nd edtion, Samir Palnitkar, SunSoft Press - A Prentice Hall Title.

- http://www.iro.umontreal.ca (source of figure)

No comments:

Post a Comment