Designing encoder in a receiver must be done before designing Viterbi decoder inside a transmitter since output of the encoder will become input of the Viterbi decoder.

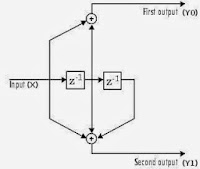

A polynomial description of a convolutional encoder describes the connections among shift registers and modulo-2 adders. The figure beside depicts a convolutional encoder that has one input, two outputs, and two shift registers. The convolutional encoder produces two bits encoded information for each bit of input information, so it is called as a rate 1/2 encoder.

Equations of the 1/2 encoder are as follow:

Y[0] = X[n] XOR X[n-1]

Y[1] = X[n] XOR X[n-1] XOR X[n-2]

The following are Verilog coding for 1/2 code rate encoder that comprises two D Flip-Flops and XOR gates.

// Module of D Flip-flop (Source: Smith, Michael J., S., 1997)

// Module name: dff.v

----------------------------------------------------------------------------

module dff(D, Q, clock, reset);

output Q;

input D, clock, reset;

parameter N = 1;

reg [N - 1: 0] Q;

wire [N - 1: 0] D;

always@posedge clock or negedge reset)

if (!reset)

Q <= 1'b0;

Q <= 1'b0;

else

Q <= D;

And Verilog codes below are Verilog coding for 1/2 code rate Encoder.

// Module of 1/2 Code Rate Encoder

// Designed by: Al-Jawie Al-Kanyarie

// Module name: Encoder1-2.v

----------------------------------------------------------------------------

module Encoder1-2(X, M0N, M1N,clock, reset);

output M0N, M1N;

input X, clock, reset;

wire X, XN_1, XN_2;

dff dff_01(X, XN_1, clock, reset); // instantiation of D Flip-flop

dff dff_02(XN_1, XN_2, clock, reset);

xor (M0N, X, XN_1);

xor (M1N, X, XN_1), XN_2;

Reference:

- Smith, Michael J., S. 1997. Application-specific integrated circuits. Addison-Wesley.

pls provide verilog test fixture for the above code.......

ReplyDelete